FPGAを生かした高速信号処理機器

-

マクロダイバーシティ受信装置

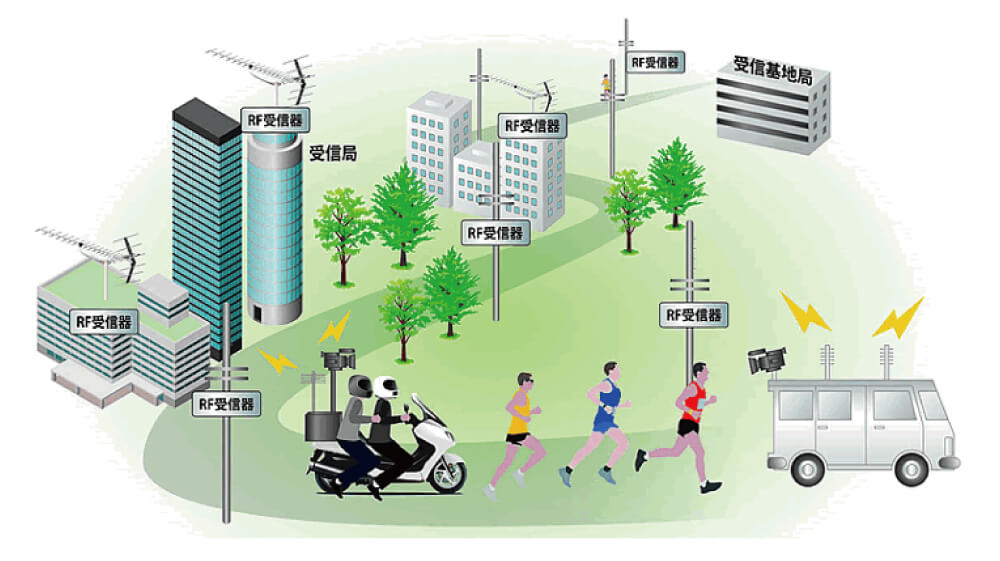

マラソン中継などでは、バイクカメラや、中継車で撮影した画像を、コースの至る所においた受信機で受信します。

その信号をオペレーターが手動で切り替えるのですが、マクロダイバーシティ受信機は、16入力までの信号から状態の良い信号を4入力選び、さらにダイバーシティ処理をすることにより、高品質な映像信号を合成します。

この処理により、不意な受信障害にも、切れない強い映像信号を出力することができます。 -

システム例:受信局から受信基地局へは光ファイバー(数~数十Km)

※1 FPU:Field Pickup Unit

※2 コース、受信システム、受信環境によります。

※3 受信アンテナ/受信器などは別途必要です

仕様概要

| 入力数 | 16入力 |

| 入力信号 | OFDM(ARIB STD-B33/B57 1K/2Kモード) |

| 入力周波数 | 130MHz/190MHz |

| 入力信号範囲 | -40dBm~0dBm |

| 入力信号間遅延補正範囲 | 最大160km相当 |

-

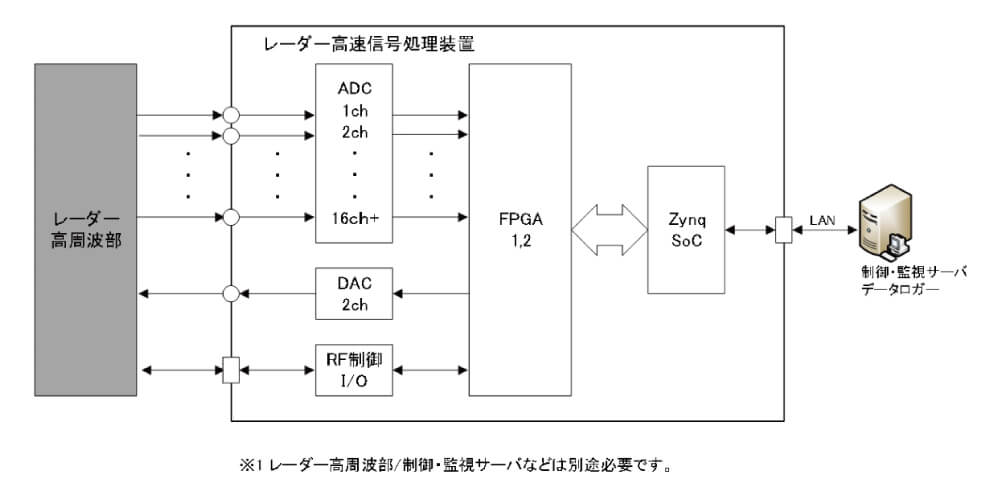

レーダー高速信号処理装置

重要インフラで使用される装置は、運用・メンテナンスを終え、次世代機への移行と置き換えが求められる。本信号処理装置もその一例であり、次世代機として現行の装置より高性能化したものとなります。

空間分解能:10倍以上(数100mを数10m以下)

時間分解能:6倍以上 (約1分を10秒以下)

空間的には、ADCを7chから16ch以上に拡張し、FPGA処理を大規模・高速化し、対象物の観測分解能を向上しています。 -

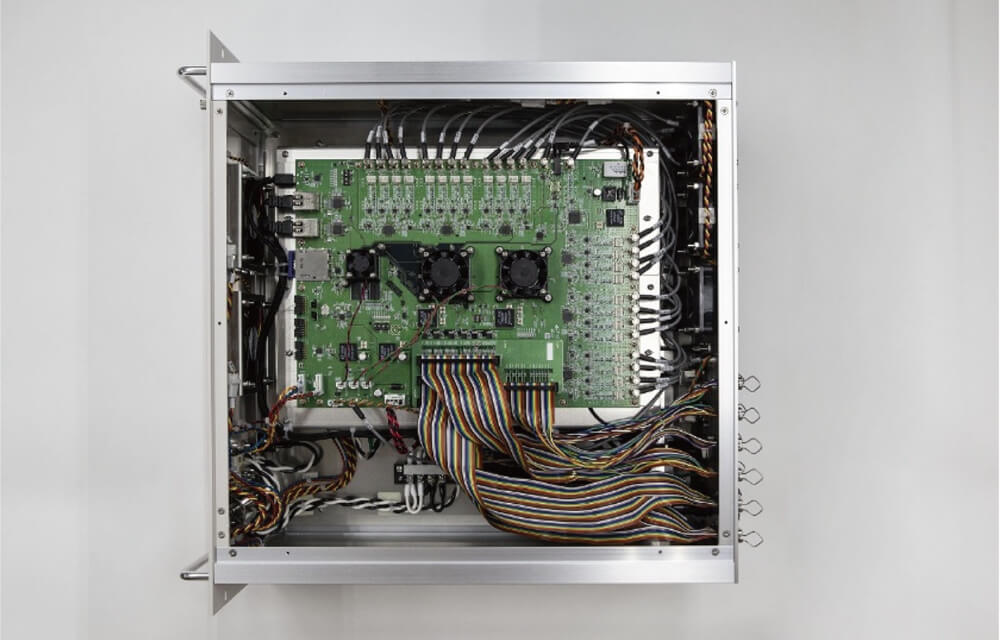

(ブロック図、内部写真)

仕様概要

| 入出力数 | 16入力/2出力 |

| 入出力周波数 | ~ 40MHz |

| 入力レベル | -70dBm~+10dBm |

| 出力レベル | 0dBm(typ.) |

| ADC/DAC | サンプリング周波数 最大125Msps 量子化分解能 16bit |

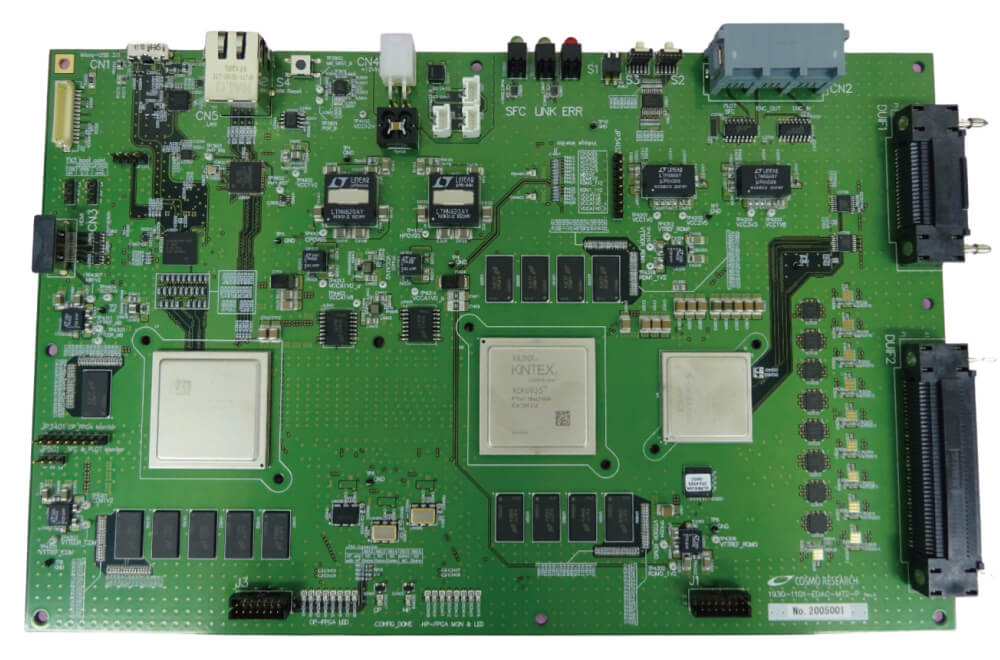

| FPGA | Xilinx Kintex UltraScale/XCKU060 2個搭載 Xilinx ZYNQ-7000/XC7Z020 1個搭載 |

| Ethernet | 1000BASE-T 2ポート搭載 |

今後、さらなる性能向上を実現するうえで、ADC,DACとFPGA/CPUが1チップ化されたRFSoCチップへの移行が期待されており、当社のRFDGボードを活用することができます。

-

画像処理エンジン

産業用生産装置の高速画像処理エンジンとして開発。

外部から入力された画像ベクタデータを高解像度で交点化し、塗りつぶし処理したラスター化されたデータを表示装置へ高速に送出することが可能です。

例えば、WQXGA画面(2560×1600)へデータ出力する場合では、毎秒最大15,000枚の画像データを表示する能力を備えています。 -